Difference between revisions of "C8051F320"

(→Features) |

|||

| Line 20: | Line 20: | ||

** Two comparators | ** Two comparators | ||

** Internal voltage reference | ** Internal voltage reference | ||

| − | ** POR/ | + | ** POR/Brown-out detector |

* USB Function Controller | * USB Function Controller | ||

** USB Specification 2.0 compliant | ** USB Specification 2.0 compliant | ||

Revision as of 08:08, 22 January 2007

Features

- High speed 8051 microcontroller core

- 70% of instructions are executed in 1 or 2 system clocks

- 24 MIPS throughput with 24 MHz clock

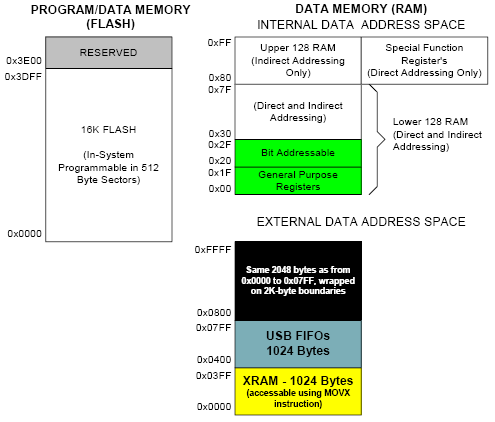

- Memory

- 2304 bytes of internal RAM (1k + 256 + 1k USB FIFO)

- 16kBytes flash, in-system programmable in 512-byte sectors

- Digital Peripherals

- 21 I/O lines and 4 input only lines, all 5V tolerant

- Hardware enhanced SPI, enhanced UART, and SMBus serial ports

- Four general purpose 16-bit counters/timers

- 16-bit programmable counter array with five capture/compare modes

- Analog Peripherals

- 10-bit ADC

- Up to 200 ksps (kilo samples per second)

- Up to 17 or 13 external single-ended or differential inputs

- VREF from external pin, internal reference or VDD

- Built-in temperature sensor

- External conversion start input

- Two comparators

- Internal voltage reference

- POR/Brown-out detector

- 10-bit ADC

- USB Function Controller

- USB Specification 2.0 compliant

- Full speed (12 Mbps) or Low speed (1.5 Mbps) operation

- Integrated clock recovery; no external crystal required for full or low speed

- Supports eight flexible endpoints

- 1kByte USB buffer memory

- Integrated transceiver; no external resistors required

- Clock Sources

- Internal Oscillator: 0.25% accuracy with Clock Recovery enabled

- External Oscillator: Crystal, RC, C or Clock

- On-chip Debug

- Non-intrusive in-system debug

- Breakpoints, single-stepping, inspect/modify memory and registers

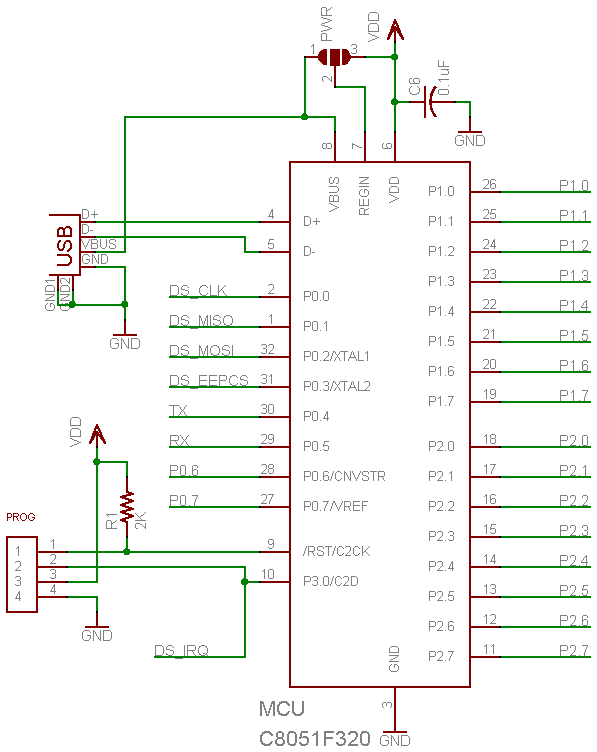

Schematic

Memory Map

See also registers